PPT VHDL Application PowerPoint Presentation, free download ID5602924

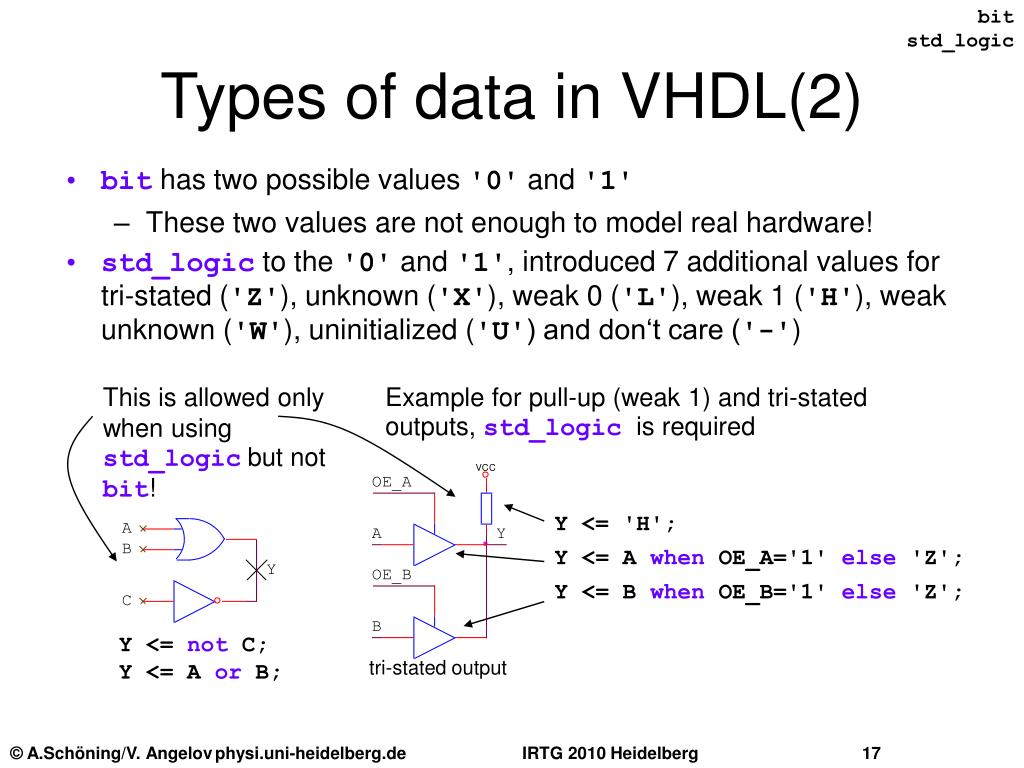

Learn about the different predefined types which can be used in VHDL and how we sack convert between them using functions and type casting. Fundamental VHDL Types. With adenine few exceptions, per signal either terminal in a VHDL designer basics consists of individual other more logical bits.

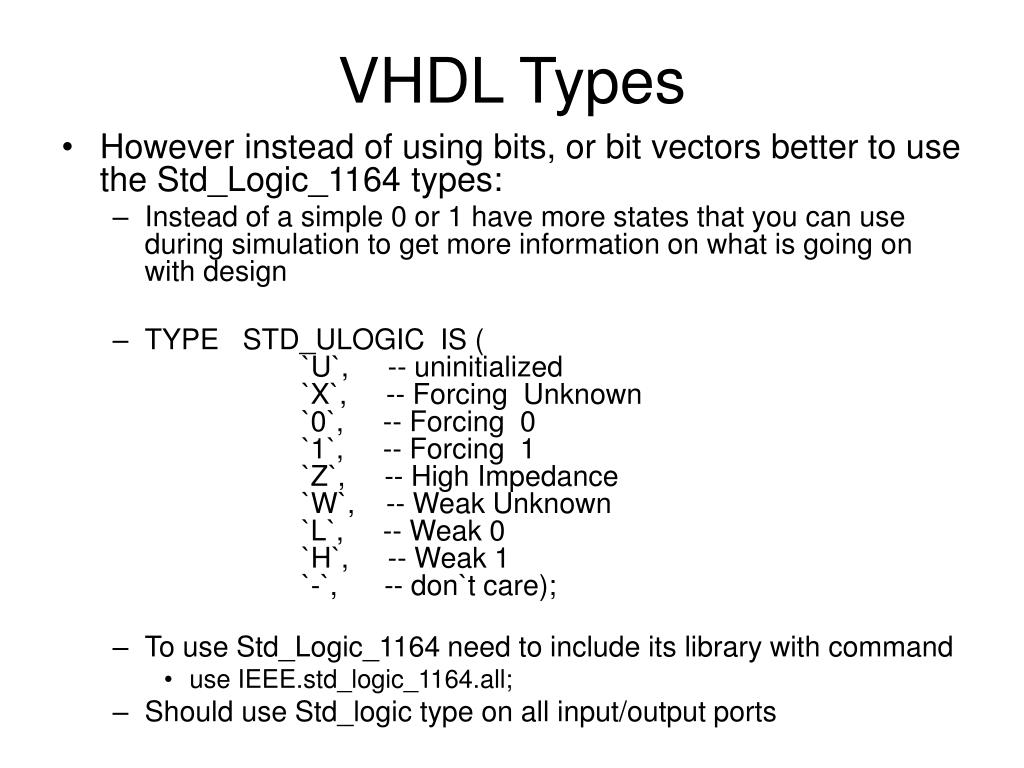

VHDL Types

In VHDL one can cast one type to another using the name of the other type e.g signal x : std_logic_vector (7 downto 0); signal y : signed (7 downto 0);. y <= signed (x) Here we use the type as if it was name of a function. Where exactly are these "cast functions" defined and why are they confused with the type name? vhdl vhdl-2008 typecast Share

PPT ECE 484 Advanced Digital Systems Design Lecture 3 Basic Language Constructs of VHDL

In recent articles we've looked at some important VHDL data types: std_logic, std_logic_vector, bit, boolean, and integer. This article will review the "signed"/"unsigned" data types, which can be used when dealing with whole numbers. Signed/Unsigned Data Types

Modeling Syntax and programming in VHDL YouTube

Std_Logic_Arith: Ambiguous Expressions. VHDL type qualifier (type_name') is a mechanism that specifies the type. of an operand or return value of a subprogram (or operator). Leaving out the ' is an error: Without ', it is type casting. Use type casting for: Recommended solution, use integer: ff cts ll.

VHDL Type Conversion BitWeenie BitWeenie

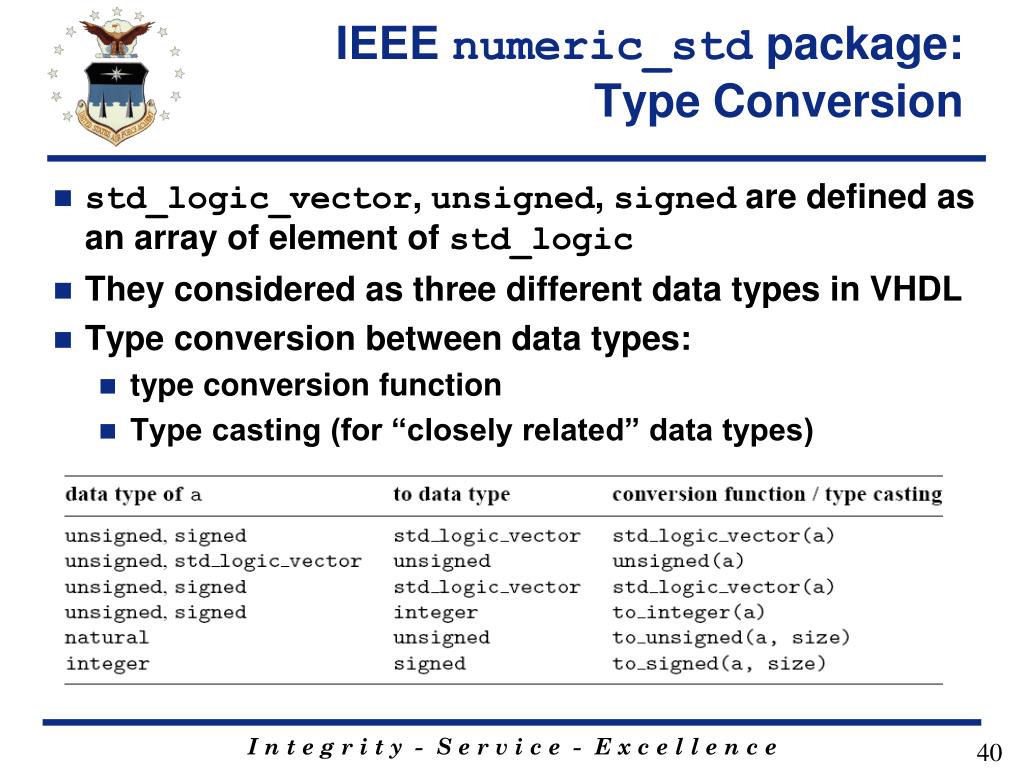

VHDL contains a set of built-in type casting operations that are commonly used with the numeric_std package to convert between std_logic_vector and unsigned/signed. Since the types unsigned/signed are based on the underlying type std_logic_vector, the conversion is simply known as casting. The following are the built-in type casting.

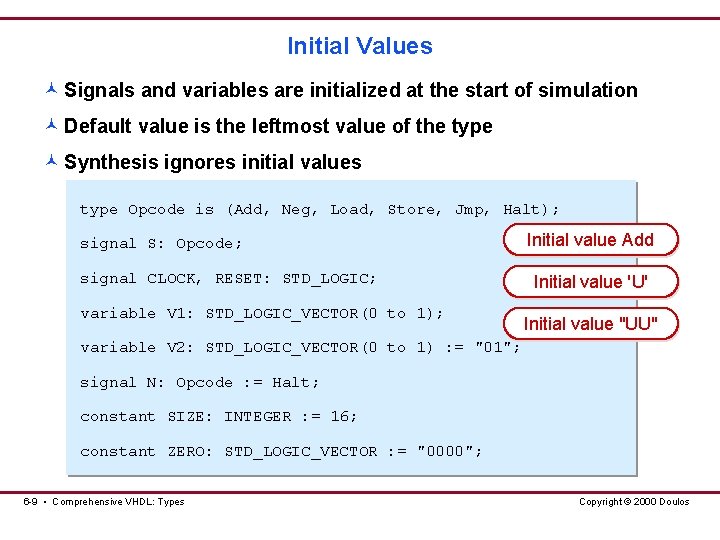

Comprehensive VHDL Module 6 Types November 2000 Types

The

PPT Introduction to VHDL for Moore Machine PowerPoint Presentation, free download ID2387766

Hierarchy, Modularity & Regularity. Break design into manageable pieces. Pieces that have well defined functionality and simple interface. Pieces that can be re-used elsewhere in the hierarchy. Gradually refine design to greater levels of detail. Set of computer aided design (CAD) tools that.

VHDL types Introduction to VHDL programming FPGAkey

Below are the most common conversions used in VHDL. The page is broken up into two sections. The first half of the page shows conversions using the Numeric_Std package file. The second half of the page shows conversions using the Std_Logic_Arith package file. It is good practice to use the Numeric_Std package as you should not use Std_Logic_Arith.

PPT Introduction to Digital Design with VHDL PowerPoint Presentation ID6952634

VHDL provides several basic data types that are fundamental to representing and manipulating digital information within a hardware design. Let's explore these basic data types: A. Boolean: In VHDL, the Boolean data type encodes logical values and has two possible values: true and false.

PPT VHDL The Very Basics PowerPoint Presentation, free download ID1186244

Unfortunately, no single function can automatically cast one signal type to another. Therefore, the use of a standard set of casting functions is important to maintain consistency between designers" - Xilinx Because VHDL is a strongly typed language, casting from one type to another is a requirement and can, at times, be difficult.

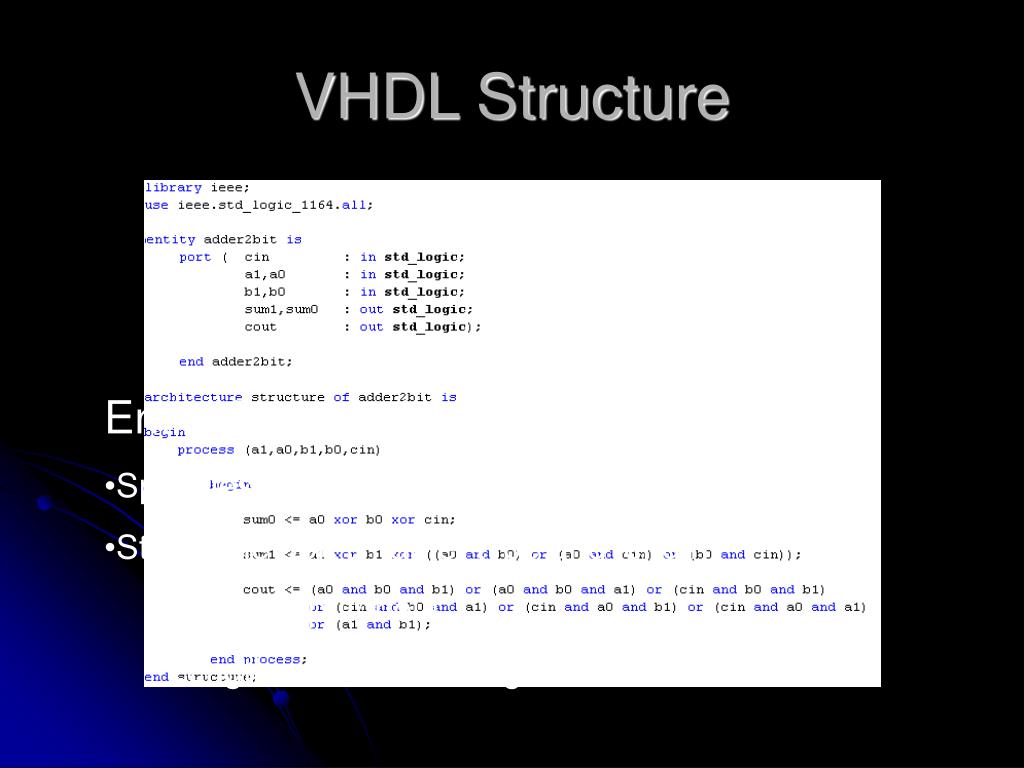

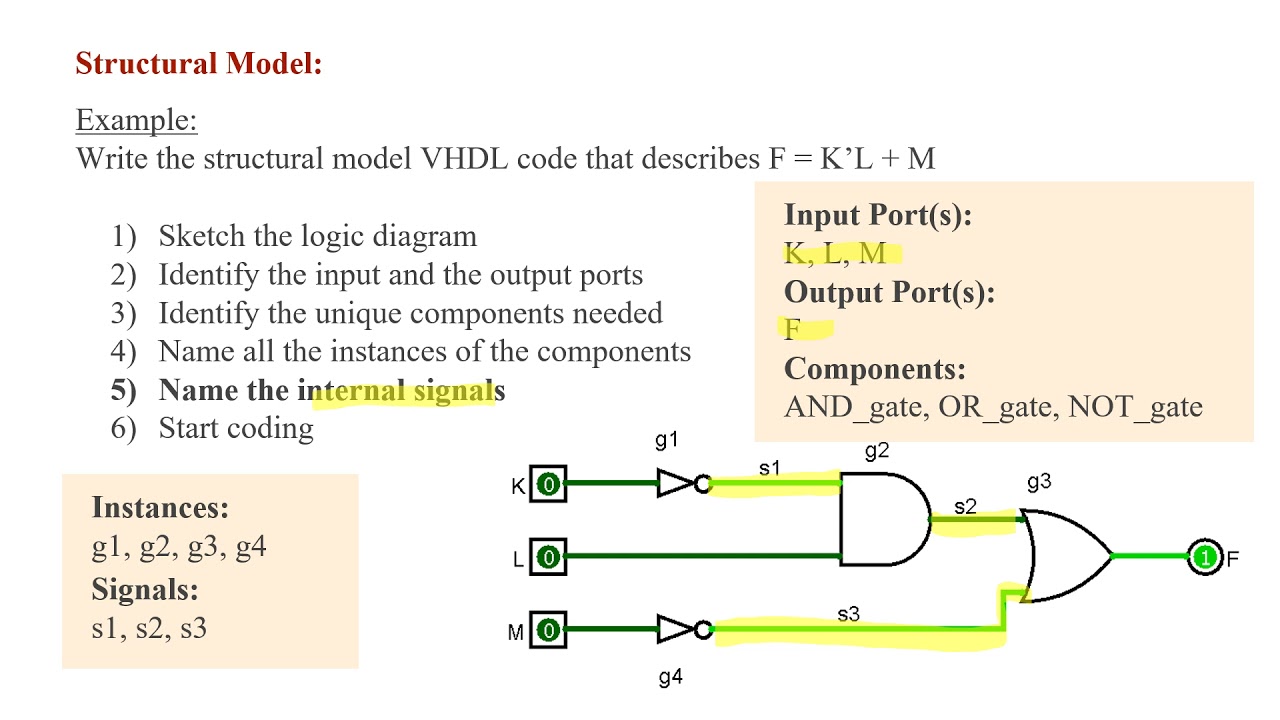

Structural VHDL

The std_logic_vector is an array of elements with std_logic data type. signal a: std_logic_vector(7 downto 0); The downto syntax puts the most significant bit (7) on the left, which is the natural representation for numbers (I rarely use the (0 to n) syntax) std_logic constants are enclosed in single quotes: '1' and '0' std_logic_vector.

PPT VHDL And Synthesis Review PowerPoint Presentation, free download ID6676668

Since a subtype is the same type as its base type, assignments between subtype and base type onjects can be made without conversion:. In VHDL-93, a new predefined subtype delay_length is defined, which can only take on positive values. subtype delay_length is time range 0 fs to time'high;.

9.4(a) Counters in VHDL w/ 1Process and Integer/TypeCasting YouTube

17 As LoneTech says, use ieee.numeric_std is your friend. You can convert a std_logic_vector to an integer, but you'll have to cast it as signed or unsigned first (as the compiler has no idea which you mean). VHDL is a strongly typed language. I've written more on this subject on my blog

001 14 Predefined DataTypes in vhdl verilog fpga YouTube

VHDL contains a set of built-in type casting operations that are commonly used with the numeric_std package to convert between std_logic_vector and unsigned/signed. Since the types unsigned and signed are based on the underlying type std_logic_vector, the conversion is simply known as casting. The following are the built-in type casting.

Introduction to VHDL Part 2 Structural Modeling YouTube

2 Casting isn't an accurate term here. Type conversion is only allowed between closely related types and your scalar type and the composite type string are not closely related (9.3.6 Type conversion). TO_STRING is a function when called returns a string representation.

VHDL Type Conversion PDF

1. Type casting and conversion functions. 2. The importance of using the appropriate type. 3. Common uses and examples. VHDL Type Cast and Conversion Functions The picture below illustrates how to convert between the most common VHDL types. Type casting is used to move between the std_logic_vector type and the signed and unsigned types.